The Semiconductor Industry's Polishing Problem

Modern computer chips are architectural marvels stacked dozens of layers high, with copper interconnects thinner than a virus. Each layer must be polished to near-atomic flatness before the next can be deposited, a process called chemical-mechanical planarization (CMP). Today, CMP relies on liquid slurries loaded with abrasive nanoparticles, chemicals that etch metal, and copious rinse water. The process works, but it is messy, wasteful, and increasingly insufficient for the sub-nanometer tolerances demanded by next-generation AI accelerators.

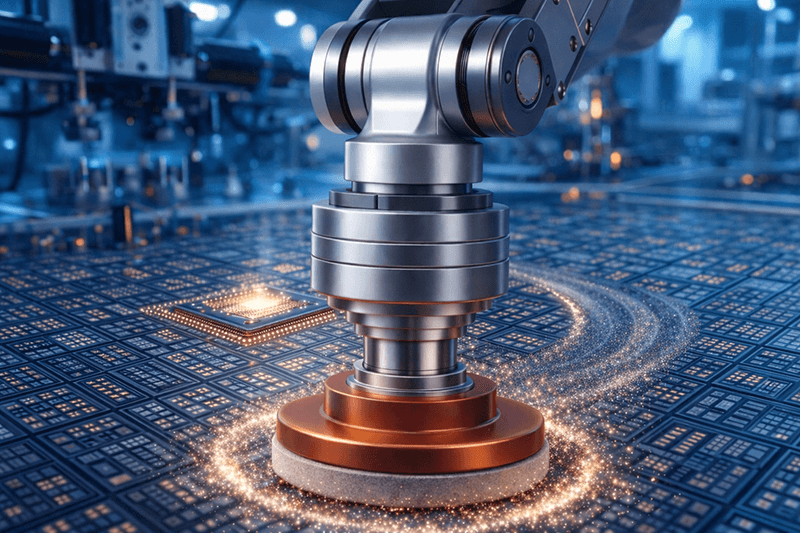

Researchers at KAIST, led by Professor Sanha Kim in the Department of Mechanical Engineering, have developed an alternative: a solid-state nano sandpaper built from vertically aligned carbon nanotubes. Published in Advanced Composites and Hybrid Materials, the technology achieves an abrasive density roughly 500,000 times higher than the finest commercial sandpaper and delivers surface finishes measured in single-digit nanometers, the thickness of just a few atoms.

How It Works

The fabrication begins with a forest of carbon nanotubes grown perpendicular to a substrate. These tubes, each only a few nanometers in diameter, are then embedded in a polyurethane matrix. A controlled etching step partially exposes the nanotube tips above the polymer surface, creating millions of uniform cutting points per square centimeter.

Because the nanotubes are anchored in the polymer rather than floating freely in a slurry, they cannot detach and scratch the workpiece. This structural stability means the nano sandpaper maintains consistent performance even after repeated use, a stark contrast to slurry-based CMP where particle size and concentration drift over time.

One Billion Grit and Counting

Sandpaper grit is a measure of abrasive particle density. Household sandpaper ranges from about 40 grit for rough wood shaping to 3,000 grit for fine automotive finishing. The KAIST nano sandpaper exceeds one billion grit, a figure so far beyond existing scales that it effectively defines a new category of surface finishing.

In head-to-head tests against conventional CMP, the nanotube approach reduced dishing defects by up to 67 percent. Dishing, an unwanted concavity that forms when softer metal areas are over-polished relative to surrounding dielectric, is one of the semiconductor industry's most persistent yield killers. Eliminating it would improve chip reliability and allow designers to shrink interconnect dimensions further.