Google is making the case for purpose-built AI hardware

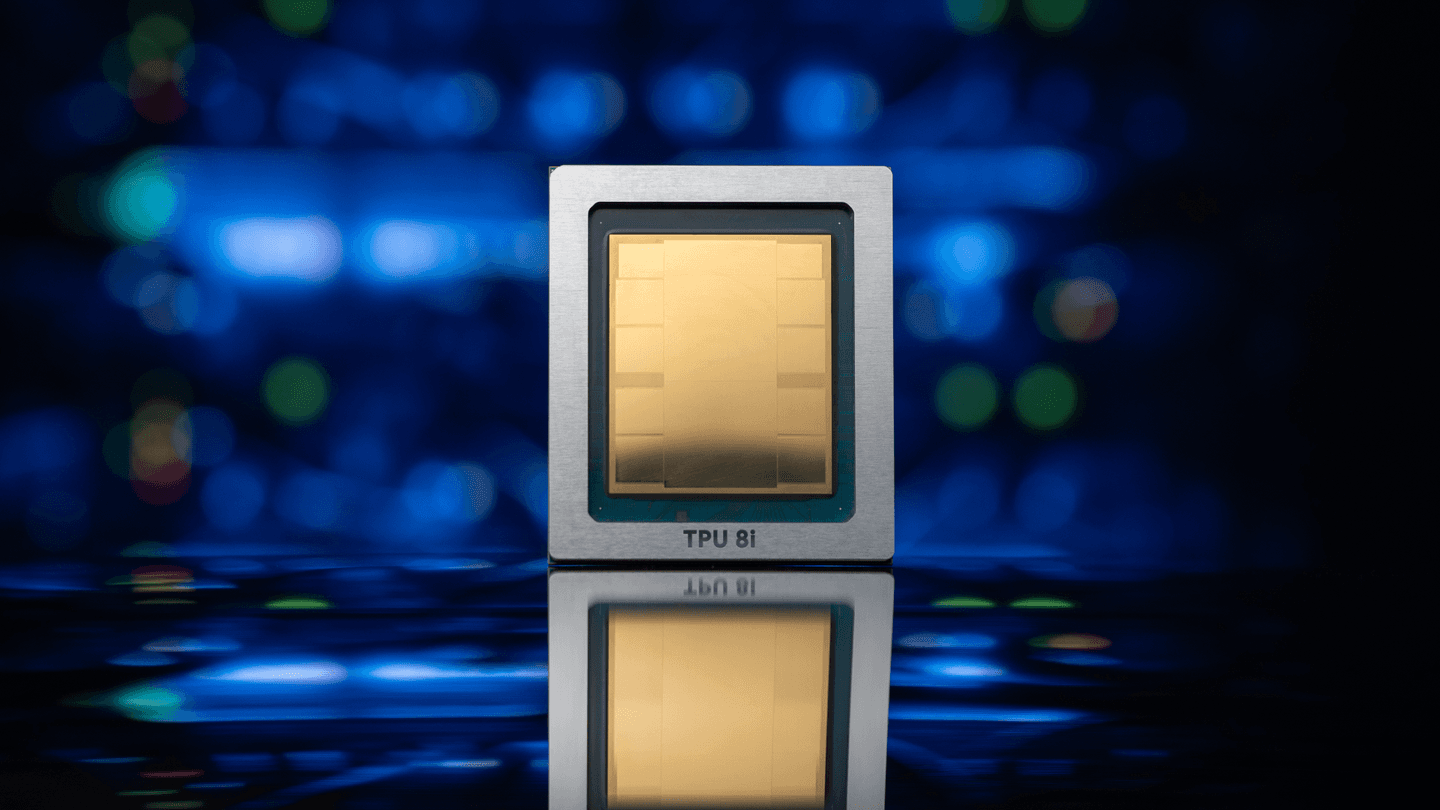

Google is again emphasizing a message that has become increasingly central to the AI industry: advanced models are no longer just a software story. They are also a hardware story, and the companies that can design, operate, and scale specialized compute infrastructure may hold a structural advantage. In a new explainer highlighting its Tensor Processing Units, or TPUs, Google says the custom chips behind many of its products were designed for a specific purpose from the start: performing the immense amount of math required by AI systems.

That framing matters because the competitive debate around artificial intelligence is shifting. Raw model quality still commands attention, but the ability to serve increasingly demanding workloads efficiently has become just as important. Training frontier systems, tuning them for new tasks, and running them continuously for users all depend on access to high-performance compute. Google’s latest TPU message is therefore not just educational branding. It is a statement about how the company wants the market to understand its position in the infrastructure race.

Why TPUs matter in Google’s strategy

According to the company, TPUs were designed more than a decade ago specifically to run AI models. That long timeline is significant. It suggests that Google’s chip effort is not a recent response to the generative AI boom but an investment that predates the current wave of demand. In practical terms, custom silicon gives Google a way to optimize around the workloads it considers most important rather than relying entirely on general-purpose processors.

The company summarizes the value proposition in simple terms: AI requires huge volumes of mathematical operations, and TPUs are designed to handle that math very quickly. In an industry where performance claims are often abstract, Google points to two concrete attributes of its newest generation: 121 exaflops of compute power and double the bandwidth of previous generations. Those specifications are the clearest signals in the material provided, and they show what Google wants potential customers and partners to focus on.

Compute power determines how much work a system can do, while bandwidth influences how efficiently data can move through that system. Both are critical for modern AI workloads, especially as models grow larger and more complex. By pairing a headline exaflop figure with a bandwidth improvement, Google is arguing not just for speed but for overall system readiness for bigger model demands.

The industry context: AI workloads keep getting heavier

Google’s message lands at a moment when infrastructure has become one of the main bottlenecks in AI. More organizations want to build or deploy sophisticated models, but access to sufficient compute remains uneven and expensive. That reality has turned data centers, chip supply, networking, and orchestration into strategic issues rather than background technical details.

Within that environment, TPUs serve several roles for Google at once. They help power the company’s own products, reinforce the technical depth of its AI platform, and support its cloud business by giving customers a differentiated option for AI workloads. Even the structure of the announcement reflects that overlap: the TPU explainer sits within Google’s cloud and AI infrastructure messaging rather than as a narrow semiconductor update.

The company also describes TPUs as being behind “the Google products you use every day.” That is a subtle but important positioning choice. Rather than presenting the chips as experimental or confined to elite research use, Google links them to mainstream services and practical reliability. The implication is that custom AI compute is already embedded in ordinary product experiences and is not merely a future bet.

Performance claims are becoming a competitive language

The way Google is talking about TPUs also reflects a broader change in how AI companies communicate. Model launches still dominate headlines, but infrastructure performance numbers increasingly function as their own form of strategic messaging. Claims about exaflops, bandwidth, and chip generations are becoming shorthand for readiness: readiness to train larger systems, run more inference, and support more customers without bottlenecks becoming debilitating.

Google’s emphasis on the newest generation of TPUs fits that pattern. The company is not disclosing every architectural detail in the supplied material, but it is making a clear argument that each generation is intended to expand what its platform can support. Doubling bandwidth relative to the previous generation is especially notable because AI performance depends not only on arithmetic capability but on how quickly data can be fed to the compute units doing the work.

That distinction is easy to miss in consumer-facing AI discussions. Bigger numbers alone do not guarantee better real-world throughput if systems are constrained elsewhere. By calling out bandwidth directly, Google is signaling that it understands the market’s focus has matured beyond simplistic compute comparisons.

What this means for the AI market

For the broader market, the TPU push highlights how much the battle over AI may hinge on full-stack integration. Companies that can pair model development with custom hardware and cloud delivery may be better positioned to manage cost, scale, and performance than those that depend on more standardized infrastructure. Google’s latest messaging does not prove superiority on its own, but it does show where the company believes its leverage lies.

It also reinforces that specialized compute is not a side issue for enterprise AI buyers. Organizations choosing an AI platform are implicitly choosing an infrastructure model, including how workloads will be accelerated and how future scale will be handled. As models become more demanding, those lower-level decisions matter more.

Google’s TPU explainer is brief, but its subtext is expansive. The company is telling the market that AI leadership is built not only in model labs and product teams, but in the chip designs and data-center systems that make large-scale machine intelligence practical. With the newest TPUs framed around 121 exaflops and doubled bandwidth, Google is presenting its hardware stack as a central answer to the next phase of AI demand.

That is likely to remain a defining theme across the sector: the winners will not just be the firms with compelling AI applications, but the ones that can sustain the compute load those applications now require.

This article is based on reporting by Google AI Blog. Read the original article.

Originally published on blog.google